# Wide Range Input, Synchronous, Step-Down DC-to-DC Controller

Data Sheet ADP1851

#### **FEATURES**

Input voltage range: 2.75 V to 20 V

Output voltage range: 0.6 V to 90%  $V_{\text{IN}}$

Maximum output current of more than 25 A

Current mode architecture

Configurable to voltage mode

$\pm 1\%$  output voltage accuracy over temperature

Voltage tracking

Programmable frequency: 200 kHz to 1.5 MHz

**Synchronization input**

Power saving mode at light load

**Precision enable input**

Power good with internal pull-up resistor

Adjustable soft start

Programmable current sense gain

Integrated bootstrap diode

Starts into a precharged load

Externally adjustable slope compensation

Suitable for any output capacitor

Overvoltage and overcurrent-limit protection

Thermal overload protection

Input undervoltage lockout (UVLO)

Available in 16-lead, 4 mm × 4 mm LFCSP

Supported by ADIsimPower design tool

#### **APPLICATIONS**

Intermediate bus and POL systems requiring sequencing and tracking, including

Telecom base station and networking Industrial and instrumentation

Medical and healthcare

#### **GENERAL DESCRIPTION**

The ADP1851 is a wide range input, dc-to-dc, synchronous buck controller capable of running from commonly used 3.3 V to 12 V (up to 20 V) voltage inputs. The device nominally operates in current mode with valley current sensing providing the fastest step response for digital loads. It can also be configured as a voltage mode controller with low noise and crosstalk for sensitive loads.

The ADP1851 is ideal in system applications requiring multiple output voltages. The ADP1851 includes a synchronization feature to eliminate beat frequencies between switching devices. It also provides accurate tracking capability between supplies and includes precision enable and power-good functions for simple, robust sequencing.

#### Rev. A Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

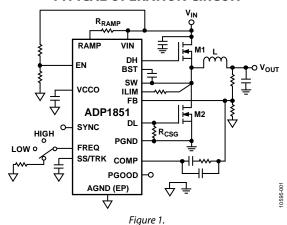

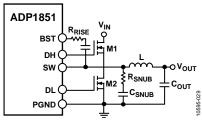

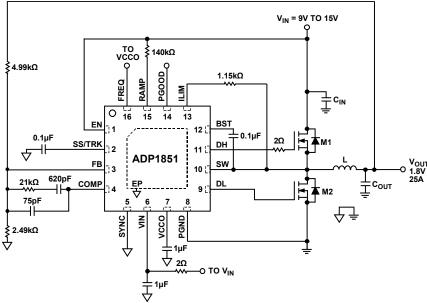

#### TYPICAL OPERATION CIRCUIT

The ADP1851 provides a high speed, high peak current gate driving capability to enable energy efficient power conversion. The device can be configured to operate in power saving mode by skipping pulses, reducing switching losses, and improving efficiency at light load and standby conditions.

The accurate current limit allows design within a narrower range of tolerances and can reduce overall converter size and cost. The ADP1851 can regulate down to 0.6 V output using a high accuracy reference with  $\pm 1\%$  tolerance over the temperature range of -40%C to +125%C.

With its wide range input voltage, the ADP1851 provides the designer with maximum flexibility for use in a variety of system configurations; loop compensation, soft start, frequency setting, power saving mode, current limit, and current sense gain can all be programmed using external components. In addition, the external RAMP resistor allows the selection of optimal slope and  $V_{\rm IN}$  feedforward in both current and voltage modes for excellent line rejection. The linear regulator and the bootstrap diode for the high-side driver are internal.

Protection features include undervoltage lockout, overvoltage, overcurrent/short circuit, and overtemperature.

# **ADP1851\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 03/09/2017

# COMPARABLE PARTS 🖳

View a parametric search of comparable parts.

### **EVALUATION KITS**

· ADP1851 Evaluation Board

### **DOCUMENTATION**

#### **Data Sheet**

ADP1851: Wide Range Input, Synchronous, Step-Down DC-to-DC Controller Data Sheet

#### **User Guides**

UG-443: Evaluation Board for the ADP1851 Step-Down DC-to-DC Controller

## TOOLS AND SIMULATIONS 🖵

- ADIsimPower<sup>™</sup> Voltage Regulator Design Tool

- ADP1851-53 Buck Designer Tool

# REFERENCE MATERIALS 🖵

#### Press

Analog Devices Expands Versatile DC-DC Switching Controller Family Featuring Current-mode and Voltagemode Configuration Options for High-current Applications

# DESIGN RESOURCES 🖵

- adp1851 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS 🖳

View all adp1851 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

# **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

# **TABLE OF CONTENTS**

| Features                                     | 1 |

|----------------------------------------------|---|

| Applications                                 | 1 |

| General Description                          | 1 |

| Typical Operation Circuit                    | 1 |

| Revision History                             | 2 |

| Simplified Block Diagram                     | 3 |

| Specifications                               | 4 |

| Absolute Maximum Ratings                     | 6 |

| ESD Caution                                  | 6 |

| Pin Configuration and Function Descriptions  | 7 |

| Typical Performance Characteristics          | 9 |

| Theory of Operation1                         | 1 |

| Control Architecture1                        | 1 |

| Oscillator Frequency1                        | 1 |

| Synchronization1                             | 2 |

| PWM and Pulse Skip Modes of Operation1       | 2 |

| Synchronous Rectifier and Dead Time1         | 3 |

| Input Undervoltage Lockout1                  | 3 |

| Internal Linear Regulator1                   | 3 |

| Overvoltage Protection1                      | 3 |

| Power Good1                                  | 3 |

| Short-Circuit and Current-Limit Protection 1 | 4 |

|                                              |   |

| REVISION HISTORY                             |   |

| 2/2017—Rev. 0 to Rev. A                      |   |

| Updated Outline Dimensions                   |   |

| Thermal Overload Protection 1           |

|-----------------------------------------|

| Applications Information 1              |

| ADIsimPower Design Tool 1               |

| Setting the Output Voltage1             |

| Soft Start                              |

| Setting the Current Limit               |

| Accurate Current-Limit Sensing1         |

| Input Capacitor Selection1              |

| VIN Pin Filter 1                        |

| Boost Capacitor Selection               |

| Inductor Selection 1                    |

| Output Capacitor Selection1             |

| MOSFET Selection                        |

| Loop Compensation—Voltage Mode1         |

| Loop Compensation—Current Mode 1        |

| Switching Noise and Overshoot Reduction |

| Voltage Tracking2                       |

| PCB Layout Guidelines2                  |

| Typical Operating Circuits              |

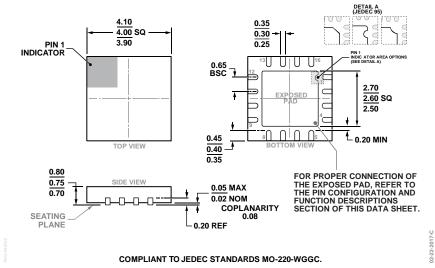

| Outline Dimensions                      |

|                                         |

| 2/2017—Rev. 0 to Rev. A    |    |

|----------------------------|----|

| Updated Outline Dimensions | 23 |

| Change to Ordering Guide   | 23 |

8/2012—Revision 0: Initial Version

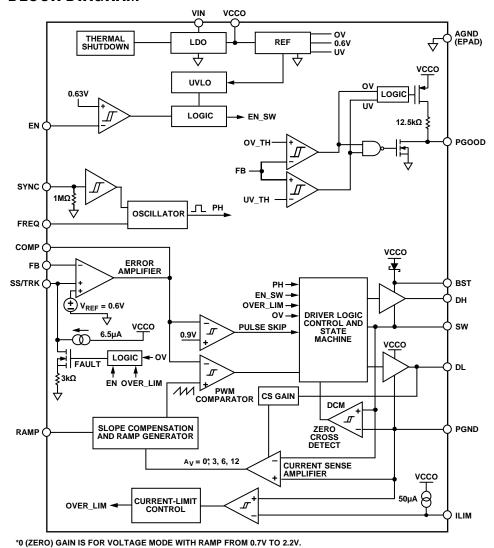

# SIMPLIFIED BLOCK DIAGRAM

Figure 2. Simplified Block Diagram

# **SPECIFICATIONS**

All limits at temperature extremes,  $T_{JMIN}$  and  $T_{JMAX}$ , are guaranteed via correlation using standard statistical quality control (SQC).  $V_{IN} = 12 \text{ V}$ . The specifications are valid for  $T_J = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ , unless otherwise specified. Typical values are at  $T_A = 25^{\circ}\text{C}$ .

Table 1.

| Parameter                                | Symbol                             | Test Conditions/Comments                                                                                                          | Min  | Тур    | Max         | Unit |

|------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|--------|-------------|------|

| POWER SUPPLY                             |                                    |                                                                                                                                   |      |        |             |      |

| Input Voltage                            | V <sub>IN</sub>                    |                                                                                                                                   | 2.75 |        | 20          | V    |

| Undervoltage Lockout Threshold           | UVLO <sub>TRSH</sub>               | V <sub>IN</sub> rising                                                                                                            | 2.55 | 2.65   | 2.75        | V    |

|                                          |                                    | V <sub>IN</sub> falling                                                                                                           | 2.35 | 2.45   | 2.50        | V    |

| Undervoltage Lockout Hysteresis          | UVLO <sub>HYST</sub>               | _                                                                                                                                 |      | 0.2    |             | V    |

| Quiescent Current                        | lin                                | $EN = V_{IN} = 12 \text{ V}$ , $V_{COMP} = 0.6 \text{ V}$ in forced pulsewidth modulation (PWM) mode (not switching), SYNC = VCCO |      | 4.2    | 5.7         | mA   |

|                                          |                                    | $EN = V_{IN} = 12 \text{ V}, V_{COMP} = 0.6 \text{ V} \text{ in PSM mode,}$<br>SYNC = AGND                                        |      | 2.5    |             | mA   |

| Shutdown Current                         | I <sub>IN_SD</sub>                 | $EN = AGND, V_{IN} = 5.5 \text{ V or } 20 \text{ V}$                                                                              |      | 100    | 200         | μΑ   |

| ERROR AMPLIFIER                          |                                    |                                                                                                                                   |      |        |             |      |

| FB Input Bias Current                    | I <sub>FB</sub>                    |                                                                                                                                   | -100 | +1     | +100        | nA   |

| Open-Loop Gain <sup>1</sup>              |                                    |                                                                                                                                   |      | 80     |             | dB   |

| Gain Bandwidth Product <sup>1</sup>      |                                    |                                                                                                                                   |      | 20     |             | MHz  |

| CURRENT SENSE AMPLIFIER GAIN             | Acs                                | Current sense gain resistor connected between DL and PGND, $R_{CSG} = 47 \text{ k}\Omega \pm 5\%$                                 | 2.6  | 3      | 3.4         | V/V  |

|                                          |                                    | Current sense gain resistor connected between DL and PGND, $R_{CSG} = 22 \text{ k}\Omega \pm 5\%$                                 | 5.2  | 6      | 6.8         | V/V  |

|                                          |                                    | Default setting, R <sub>CSG</sub> = open                                                                                          | 10.5 | 12     | 13.5        | V/V  |

|                                          |                                    | Voltage mode operation, resistor connected between DL and PGND, $R_{CSG} = 100 \text{ k}\Omega \pm 5\%$                           |      | 0      |             | V/V  |

| OUTPUT CHARACTERISTICS                   |                                    |                                                                                                                                   |      |        |             |      |

| Feedback Accuracy Voltage                | $V_{FB}$                           | $T_{J} = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                                             | 597  | 600    | 603         | mV   |

|                                          |                                    | $T_1 = -40^{\circ}\text{C to } + 125^{\circ}\text{C}$                                                                             | 594  | 600    | 606         | mV   |

| Line Regulation of PWM                   | ΔV <sub>FR</sub> /ΔV <sub>IN</sub> | 1] = -40 C to +125 C                                                                                                              | 351  | ±0.015 | 000         | %/V  |

| Load Regulation of PWM <sup>1</sup>      | $\Delta V_{FB}/\Delta V_{COMP}$    | V <sub>COMP</sub> range = 0.9 V to 2.2 V                                                                                          |      | ±0.013 |             | %    |

| OSCILLATOR                               | 7 A FRY 7 A COWL                   | VCOMPTATIGE - 0.9 V to 2.2 V                                                                                                      |      | ±0.5   |             | 70   |

| Frequency                                | fosc                               | $R_{FREO} = 332 \text{ k}\Omega \text{ to AGND}$                                                                                  | 170  | 200    | 230         | kHz  |

| rrequency                                | TOSC                               | $R_{FREQ} = 78.7 \text{ k}\Omega \text{ to AGND}$                                                                                 | 720  | 800    | 880         | kHz  |

|                                          |                                    | $R_{FREO} = 40.2 \text{ k}\Omega \text{ to AGND}$                                                                                 | 1275 | 1500   | 1725        | kHz  |

|                                          |                                    | FREQ connected to AGND                                                                                                            | 240  | 300    | 360         | kHz  |

|                                          |                                    | FREQ connected to VCCO                                                                                                            | -    |        |             | kHz  |

| CVNC In part From your part Pop and      | _                                  |                                                                                                                                   | 480  | 600    | 720<br>1725 | kHz  |

| SYNC Input Frequency Range <sup>1</sup>  | f <sub>SYNC</sub>                  | $R_{\text{FREQ}}$ range from 332 k $\Omega$ to 40.2 k $\Omega$                                                                    | 170  |        | 1725        |      |

| SYNC Input Pulse Width <sup>1</sup>      | tsyncmin                           |                                                                                                                                   | 100  | _      |             | ns   |

| SYNC Pin Capacitance to AGND             | C <sub>SYNC</sub>                  |                                                                                                                                   |      | 5      |             | pF   |

| LINEAR REGULATOR                         |                                    |                                                                                                                                   | 4.5  |        |             | .,   |

| VCCO Output Voltage                      |                                    | I <sub>VCCO</sub> = 100 mA                                                                                                        | 4.7  | 5.0    | 5.3         | V    |

| VCCO Load Regulation                     |                                    | $I_{VCCO} = 0 \text{ mA to } 100 \text{ mA}$                                                                                      |      | 35     |             | mV   |

| VCCO Line Regulation                     |                                    | $V_{IN} = 5.5 \text{ V to } 20 \text{ V}, I_{VCCO} = 20 \text{ mA}$                                                               |      | 10     |             | mV   |

| VCCO Current Limit <sup>1</sup>          |                                    | VCCO drops to 4 V from 5 V                                                                                                        |      | 350    |             | mA   |

| VCCO Short-Circuit Current <sup>1</sup>  |                                    | VCCO < 0.5 V                                                                                                                      |      | 370    | 400         | mA   |

| VIN to VCCO Dropout Voltage <sup>2</sup> | V <sub>DROPOUT</sub>               | $I_{VCCO} = 100 \text{ mA}, V_{IN} \le 5 \text{ V}$                                                                               |      | 0.33   |             | V    |

| LOGIC INPUTS                             |                                    |                                                                                                                                   |      |        |             |      |

| EN Threshold Voltage                     |                                    | EN rising                                                                                                                         | 0.57 | 0.63   | 0.68        | V    |

| EN Hysteresis                            |                                    |                                                                                                                                   |      | 0.03   |             | V    |

| EN Input Leakage Current                 | I <sub>EN</sub>                    | $V_{IN} = 2.75 \text{ V to } 20 \text{ V}$                                                                                        |      | 1      | 200         | nA   |

| Parameter                                                          | Symbol                  | Test Conditions/Comments                                                        | Min   | Тур  | Max   | Unit |

|--------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------|-------|------|-------|------|

| SYNC Logic Input Low                                               |                         |                                                                                 |       |      | 1.3   | V    |

| SYNC Logic Input High                                              |                         |                                                                                 | 1.9   |      |       | V    |

| SYNC Input Pull-Down Resistance                                    | R <sub>SYNC</sub>       |                                                                                 |       | 1    |       | ΜΩ   |

| GATE DRIVERS                                                       |                         |                                                                                 |       |      |       |      |

| DH Rise Time                                                       |                         | $C_{DH} = 3 \text{ nF, } V_{BST} - V_{SW} = 5 \text{ V}$                        |       | 16   |       | ns   |

| DH Fall Time                                                       |                         | $C_{DH} = 3 \text{ nF, } V_{BST} - V_{SW} = 5 \text{ V}$                        |       | 14   |       | ns   |

| DL Rise Time                                                       |                         | $C_{DL} = 3 \text{ nF}$                                                         |       | 16   |       | ns   |

| DL Fall Time                                                       |                         | $C_{DL} = 3 \text{ nF}$                                                         |       | 14   |       | ns   |

| DH to DL Dead Time                                                 |                         | External 3 nF connected to DH and DL                                            |       | 25   |       | ns   |

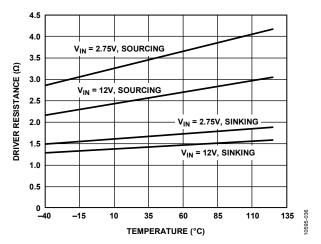

| DH or DL Driver R <sub>ON</sub> , Sourcing<br>Current <sup>1</sup> | Ron_source              | Sourcing 2 A with a 100 ns pulse                                                |       | 2    |       | Ω    |

|                                                                    |                         | Sourcing 1 A with a 100 ns pulse, $V_{IN} = 3 \text{ V}$                        |       | 2.3  |       | Ω    |

| DH or DL Driver R <sub>ON</sub> , Tempco                           | TC <sub>RON</sub>       | $V_{IN} = 3 \text{ V or } 12 \text{ V}$                                         |       | 0.3  |       | %/°C |

| DH or DL Driver R <sub>ON</sub> , Sinking<br>Current <sup>1</sup>  | Ron_sink                | Sinking 2 A with a 100 ns pulse                                                 |       | 1.5  |       | Ω    |

|                                                                    |                         | Sinking 1 A with a 100 ns pulse, $V_{IN} = 3 \text{ V}$                         |       | 2    |       | Ω    |

| DH Maximum Duty Cycle <sup>1</sup>                                 |                         | fosc = 300 kHz                                                                  | 90    |      |       | %    |

|                                                                    |                         | $f_{OSC} = 1500 \text{ kHz}$                                                    | 50    |      |       | %    |

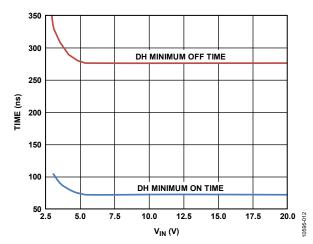

| Minimum DH On Time                                                 |                         | fosc = 200 kHz to 1500 kHz                                                      |       |      | 85    | ns   |

| Minimum DH Off Time                                                |                         | $f_{OSC} = 200 \text{ kHz to } 1500 \text{ kHz}$                                |       |      | 345   | ns   |

| Minimum DL On Time                                                 |                         | fosc = 200 kHz to 1500 kHz                                                      |       |      | 295   | ns   |

| COMP VOLTAGE RANGE                                                 |                         |                                                                                 |       |      |       |      |

| COMP Pulse Skip Threshold                                          | V <sub>COMP,THRES</sub> | In pulse skip mode (PSM)                                                        |       | 0.9  |       | V    |

| COMP Clamp High Voltage                                            | V <sub>COMP,HIGH</sub>  |                                                                                 | 2.2   |      |       | V    |

| THERMAL SHUTDOWN                                                   |                         |                                                                                 |       |      |       |      |

| Thermal Shutdown Threshold                                         | T <sub>TMSD</sub>       |                                                                                 |       | 155  |       | °C   |

| Thermal Shutdown Hysteresis                                        |                         |                                                                                 |       | 20   |       | °C   |

| OVERVOLTAGE AND POWER-GOOD THRESHOLDS                              |                         |                                                                                 |       |      |       |      |

| FB Overvoltage Threshold                                           | Vov                     | V <sub>FB</sub> rising                                                          | 0.630 | 0.65 | 0.670 | V    |

| FB Overvoltage Hysteresis                                          |                         |                                                                                 |       | 18   |       | mV   |

| FB Undervoltage Threshold                                          | V <sub>UV</sub>         | V <sub>FB</sub> falling                                                         | 0.525 | 0.55 | 0.575 | V    |

| FB Undervoltage Hysteresis                                         |                         |                                                                                 |       | 15   |       | mV   |

| SOFT START/TRACK                                                   |                         |                                                                                 |       |      |       |      |

| SS/TRK Output Current                                              | I <sub>SS</sub>         | During startup                                                                  | 4.6   | 6.5  | 8.4   | μΑ   |

| SS/TRK Pull-Down Resistor                                          |                         | During a fault condition                                                        |       | 3    |       | kΩ   |

| SS/TRK Input Voltage Range <sup>1</sup>                            |                         |                                                                                 | 0     |      | 5     | V    |

| FB to SS/TRK Offset                                                |                         | $V_{SS/TRK} = 0.1 \text{ V to } 0.6 \text{ V}$ ; offset = $V_{FB} - V_{SS/TRK}$ | -10   |      | +10   | mV   |

| PGOOD                                                              |                         |                                                                                 |       |      |       |      |

| PGOOD Pull-Up Resistor                                             | R <sub>PGOOD</sub>      | Internal pull-up resistor to VCCO                                               |       | 12.5 |       | kΩ   |

| PGOOD Delay                                                        | 1,1,000                 |                                                                                 |       | 12.5 |       | μs   |

| Overvoltage or Undervoltage                                        |                         | Minimum duration required to trigger the                                        |       | 10   |       | μs   |

| Minimum Duration                                                   |                         | PGOOD signal                                                                    |       | .5   |       | ۳3   |

| ILIM Threshold Voltage <sup>1</sup>                                |                         | Relative to PGND                                                                | -5    | 0    | +5    | mV   |

| ILIM Output Current                                                |                         | ILIM = PGND                                                                     | 45    | 50   | 55    | μΑ   |

| Current Sense Blanking Period                                      |                         | After DL goes high; current limit is not sensed during this period              |       | 100  |       | ns   |

| INTEGRATED RECTIFIER<br>(BOOST DIODE) RESISTANCE                   |                         | At 20 mA forward current                                                        |       | 16   |       | Ω    |

| ZERO CURRENT CROSS OFFSET (SW TO PGND) <sup>1</sup>                |                         | In pulse skip mode only; fosc = 300 kHz                                         | 0     | 2    | 4     | mV   |

$<sup>^{1}</sup>$  Guaranteed by design.  $^{2}$  Connect VIN to VCCO when  $V_{\text{IN}}$  < 5.5 V.

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                          | Rating                 |

|----------------------------------------------------|------------------------|

| VIN, EN, RAMP                                      | 21 V                   |

| FB, COMP, SS/TRK, FREQ, SYNC, VCCO, PGOOD          | -0.3 V to +6 V         |

| ILIM, SW to PGND                                   | −0.3 V to +21 V        |

| BST, DH to PGND                                    | −0.3 V to +28 V        |

| DL to PGND                                         | -0.3 V to VCCO + 0.3 V |

| BST to SW                                          | −0.3 V to +6 V         |

| BST to PGND, 20 ns Transients                      | 32 V                   |

| SW to PGND, 20 ns Transients                       | 25 V                   |

| DL, SW, ILIM to PGND, 20 ns<br>Negative Transients | -8 V                   |

| PGND to AGND                                       | −0.3 V to +0.3 V       |

| PGND to AGND, 20 ns Transients                     | −8 V to +4 V           |

| $\theta_{JA}$ (Natural Convection) <sup>1, 2</sup> | 40°C/W                 |

| Operating Junction Temperature Range <sup>3</sup>  | −40°C to +125°C        |

| Storage Temperature Range                          | −65°C to +150°C        |

| Maximum Soldering Lead Temperature                 | 260°C                  |

<sup>&</sup>lt;sup>1</sup> Measured with exposed pad attached to PCB.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Absolute maximum ratings apply individually only, not in combination. Unless otherwise specified, all other voltages are referenced to AGND.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

$<sup>^2</sup>$  Junction-to-ambient thermal resistance ( $\theta_{JA}\!)$  of the package was calculated or simulated on a multilayer PCB.

$<sup>^3</sup>$ The junction temperature (T<sub>J</sub>) of the device is dependent on the ambient temperature (T<sub>A</sub>), the power dissipation of the device (P<sub>D</sub>), and the junction-to-ambient thermal resistance of the package ( $\theta_{JA}$ ). Maximum junction temperature is calculated from the ambient temperature and power dissipation using the formula  $T_J = T_A + P_D \times \theta_{JA}$ .

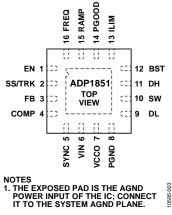

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 3. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | EN       | Enable Input. Drive EN high to turn the controller on, and drive EN low to turn the controller off. Tie EN to $V_{IN}$ for automatic startup. For a precision UVLO, connect an appropriately sized resistor divider from $V_{IN}$ to AGND, and tie the midpoint to this pin.                                                                                                                                                                                               |

| 2       | SS/TRK   | Soft Start/Tracking Input. Connect a capacitor from SS/TRK to AGND to set the soft start time. This node is internally pulled up to VCCO through a 6.5 $\mu$ A current source. Use this pin as the TRK input for tracking an external voltage during startup.                                                                                                                                                                                                              |

| 3       | FB       | Output Voltage Feedback Input. Connect this pin to an output via a resistor divider.                                                                                                                                                                                                                                                                                                                                                                                       |

| 4       | COMP     | Compensation Node. Output of the error amplifier. Connect a resistor/capacitor (RC) network from COMP to FB to compensate the regulation control loop.                                                                                                                                                                                                                                                                                                                     |

| 5       | SYNC     | Frequency Synchronization Input. This pin accepts an external clock signal with a frequency close to $1\times$ the internal oscillator frequency, $f_{OSC}$ , set by the FREQ pin. The controller operates in forced PWM mode when a periodic clock signal is detected at SYNC or when SYNC is high (connected to VCCO). The resulting switching frequency is $1\times$ the SYNC frequency. When SYNC is low or left floating, the controller operates in pulse skip mode. |

| 6       | VIN      | Input Voltage. Connect to main power supply. Bypass with a 1 $\mu F$ or larger ceramic capacitor connected as close as possible to this pin and AGND.                                                                                                                                                                                                                                                                                                                      |

| 7       | vcco     | Output of the Internal Low Dropout (LDO) Regulator. The internal circuitry and gate drivers are powered from VCCO. Bypass VCCO to AGND with a 1 $\mu$ F or larger ceramic capacitor. The VCCO output remains active even when EN is low. For operations at $V_{IN}$ below 5.5 V, VIN can be connected to VCCO. Do not use the LDO to power other auxiliary system loads.                                                                                                   |

| 8       | PGND     | Power Ground. Ground for internal driver. Differential current is sensed between SW and PGND.                                                                                                                                                                                                                                                                                                                                                                              |

| 9       | DL       | Low-Side Synchronous Rectifier Gate Driver Output. To program the gain of the current sense amplifier in a current mode or to set voltage mode control, connect a resistor between DL and PGND. This pin is capable of driving MOSFETs with a total input capacitance up to 20 nF.                                                                                                                                                                                         |

| 10      | SW       | Power Switch Node/Current Sense Amplifier Input. Connect this pin to the source of the high-side N-channel MOSFET and the drain of the low-side N-channel MOSFET. Differential current is sensed between SW and PGND.                                                                                                                                                                                                                                                      |

| 11      | DH       | High-Side Switch Gate Driver Output. This pin is capable of driving MOSFETs with a total input capacitance up to 20 nF.                                                                                                                                                                                                                                                                                                                                                    |

| 12      | BST      | Bootstrapped Upper Rail of High-Side Internal Driver. Connect a multilayer ceramic capacitor (MLCC) with a value from 0.1 $\mu$ F to 0.22 $\mu$ F between BST and SW. An internal boost diode rectifier is connected between VCCO and BST.                                                                                                                                                                                                                                 |

| 13      | ILIM     | Current-Limit Sense Comparator Inverting Input. Connect a resistor between ILIM and SW to set the current-limit offset. For accurate current-limit sensing, connect ILIM to a current sense resistor at the source of the low-side MOSFET.                                                                                                                                                                                                                                 |

| 14      | PGOOD    | Power Good. PGOOD is the open-drain power-good indicator logic output with an internal 12.5 k $\Omega$ resistor connected between PGOOD and VCCO.                                                                                                                                                                                                                                                                                                                          |

| 15      | RAMP     | Programmable Current Setting for Slope Compensation. Connect a resistor from RAMP to $V_{IN}$ . The voltage at RAMP is 0.2 V during operation. This pin is high impedance when the controller is disabled.                                                                                                                                                                                                                                                                 |

| Pin No. | Mnemonic    | Description                                                                                                                                                                                                                                                        |

|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16      | FREQ        | Internal Oscillator Frequency, f <sub>OSC</sub> . Sets the desired operating frequency between 200 kHz and 1.5 MHz with one resistor between FREQ and AGND. Connect FREQ to AGND for a preprogrammed 300 kHz, or tie FREQ to VCCO for 600 kHz operating frequency. |

|         | EPAD (AGND) | Exposed Pad, Analog Ground. The exposed pad is the AGND power input of the IC. Connect the exposed pad to the system AGND plane.                                                                                                                                   |

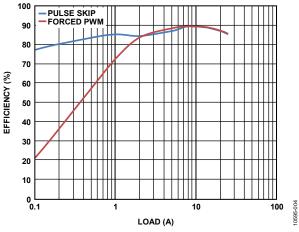

# TYPICAL PERFORMANCE CHARACTERISTICS

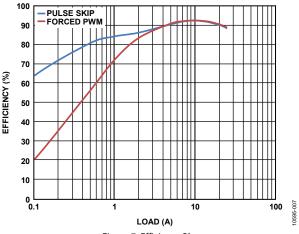

Figure 4. Efficiency Plot 12 V<sub>IN</sub> to 1.8 V<sub>OUT</sub>, 600 kHz (see Figure 34 for Circuit)

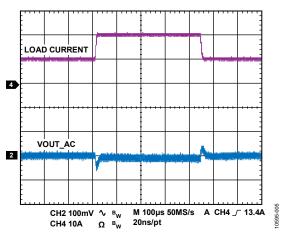

Figure 5. 10 A to 20 A Load Step, 12 V<sub>IN</sub> to 1.8 V<sub>OUT</sub>, 600 kHz, Current Mode

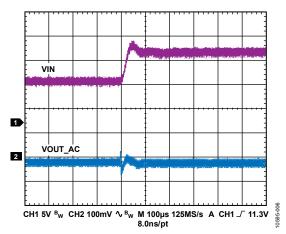

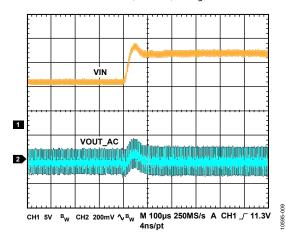

Figure 6. 9 V to 15 V Line Step, 1.8 V<sub>OUT</sub>, 20 A Load, Current Mode

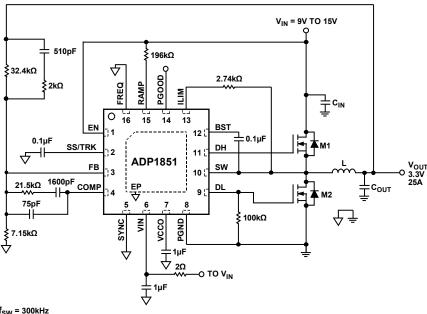

Figure 7. Efficiency Plot 12 V<sub>IN</sub> to 3.3 V<sub>OUT</sub>, 300 kHz (see Figure 35 for Circuit)

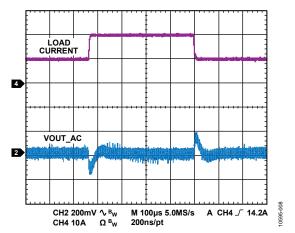

Figure 8. 10 A to 20 A Load Step, 12 V<sub>IN</sub> to 3.3 V<sub>OUT</sub>, 300 kHz, Voltage Mode

Figure 9. 9 V to 15 V Line Step, 3.3 V<sub>OUT</sub>, 15 A Load, Voltage Mode

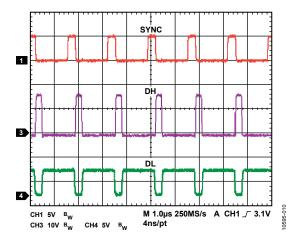

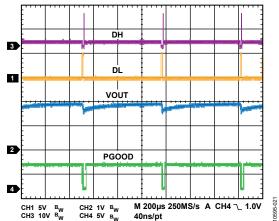

Figure 10. Synchronization,  $f_{SYNC} = 600 \text{ kHz}$

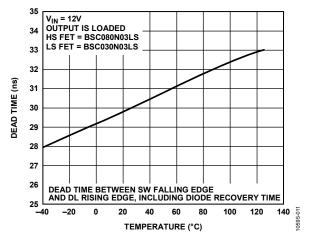

Figure 11. Dead Time vs. Temperature

Figure 12. Typical DH Minimum On Time and Off Time

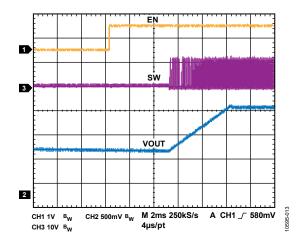

Figure 13. Soft Start with Precharged Output, 1.8  $V_{OUT}$  Forced PWM Mode

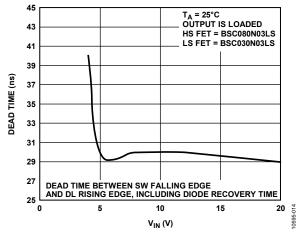

Figure 14. Dead Time vs. V<sub>IN</sub>

Figure 15. Driver Resistance vs. Temperature

### THEORY OF OPERATION

The ADP1851 is a fixed frequency, step-down, synchronous switching controller with integrated drivers and bootstrapping for external N-channel power MOSFETs. The current mode control loop can also be configured to voltage mode. The controller can be set to operate in pulse skip mode for power saving at light loads or in forced PWM mode. The ADP1851 includes programmable soft start, output overvoltage protection, programmable current limit, power good, and tracking functions. The controller can operate at a switching frequency between 200 kHz and 1.5 MHz that is programmed with a resistor or synchronized to an external clock.

#### **CONTROL ARCHITECTURE**

The ADP1851 is based on a fixed frequency, emulated peak current mode, PWM control architecture. The inductor current is sensed by the voltage drop measured across the external low-side MOSFET, R<sub>DSON</sub>, or across the sense resistor placed in series between the low-side MOSFET source and the power ground. The current is sensed during the off period of the switching cycle and is conditioned with the internal current sense amplifier.

The gain of the current sense amplifier is programmable to 3 V/V, 6 V/V, or 12 V/V during the controller power-up initialization before the device starts switching. A 47 k $\Omega$  resistor between DL and PGND programs a gain of 3 V/V; a 22 k $\Omega$  resistor sets a gain of 6 V/V. Without a resistor, the gain is programmed to 12 V/V.

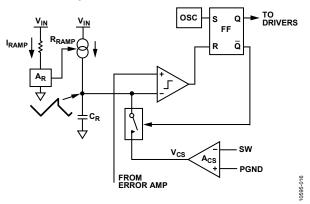

The output signal of the current sense amplifier is held, added to the emulated current ramp in the next switching cycle during the DH on time, and fed into the PWM comparator, as shown in Figure 16. This signal is compared with the COMP signal from the error amplifier and resets the flip-flop, which generates the PWM pulse. If voltage mode control is selected by placing a 100  $k\Omega$  resistor between DL and PGND, the emulated current ramp is fed to the PWM comparator without adding the current sense signal.

Figure 16. Simplified Control Architecture

As shown in Figure 16, the emulated current ramp is generated inside the IC, but offers programmability through the RAMP pin. Selecting an appropriate value resistor to connect between  $V_{\rm IN}$  and the RAMP pin programs a desired slope compensation value and, at the same time, provides a  $V_{\rm IN}$  feedforward feature. Control logic enforces antishoot-through operation to limit cross-conduction of the internal drivers and external MOSFETs.

#### **OSCILLATOR FREQUENCY**

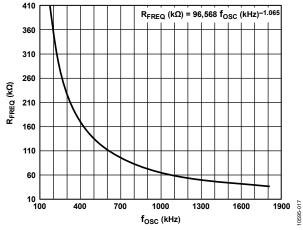

The internal oscillator frequency, which ranges from 200 kHz to 1.5 MHz, is set by an external resistor,  $R_{\text{FREQ}}$ , at the FREQ pin. Some common  $f_{\text{OSC}}$  values are shown in Table 4, and a graphical relationship is shown in Figure 17. For example, a 78.7 k $\Omega$  resistor sets the oscillator frequency to 800 kHz. Connecting FREQ to AGND or FREQ to VCCO sets the oscillator frequency to 300 kHz or 600 kHz, respectively. For other frequencies that are not listed in Table 4, the values of  $R_{\text{FREQ}}$  and  $f_{\text{OSC}}$  can be obtained from Figure 17, or use the following empirical formula to calculate these values:

$$R_{FREQ}(k\Omega) = 96,568 \times f_{OSC}(kHz)^{-1.065}$$

**Table 4. Setting the Oscillator Frequency**

| ruble is betting the obeliator frequency |                            |  |  |

|------------------------------------------|----------------------------|--|--|

| R <sub>FREQ</sub>                        | f <sub>osc</sub> (Typical) |  |  |

| 332 kΩ                                   | 200 kHz                    |  |  |

| 78.7 kΩ                                  | 800 kHz                    |  |  |

| 60.4 kΩ                                  | 1000 kHz                   |  |  |

| 51 kΩ                                    | 1200 kHz                   |  |  |

| 40.2 kΩ                                  | 1500 kHz                   |  |  |

| FREQ to AGND                             | 300 kHz                    |  |  |

| FREQ to VCCO                             | 600 kHz                    |  |  |

Figure 17. R<sub>FREQ</sub> vs. f<sub>OSC</sub>

#### **SYNCHRONIZATION**

The switching frequency of the ADP1851 can be synchronized to an external clock signal by connecting it to the SYNC pin. The internal oscillator frequency, programmed by the resistor at the FREQ pin, must be set close to the external clock frequency; therefore, the external clock frequency can vary between  $0.85\times$  and  $1.3\times$  the internal clock set. The resulting switching frequency is  $1\times$  the external SYNC frequency. When synchronized, the ADP1851 operates in PWM mode.

When an external clock is detected at the first SYNC edge, the internal oscillator is reset, and the clock control shifts to SYNC. The SYNC edges then trigger subsequent clocking of the PWM outputs. The DH rising edge appears approximately 100 ns after the corresponding SYNC edge, and the frequency is locked to the external signal. If the external SYNC signal disappears during operation, the ADP1851 reverts to its internal oscillator. When the SYNC function is used, it is recommended that a pull-up resistor be connected from SYNC to VCCO so that when the SYNC signal is lost, the ADP1851 continues to operate in PWM mode.

#### **PWM AND PULSE SKIP MODES OF OPERATION**

The SYNC pin is a multifunctional pin. PWM mode is enabled when SYNC is connected to VCCO or a high logic. When SYNC is connected to ground or left floating, pulse skip mode is enabled. Switching SYNC from low to high or high to low on the fly causes the controller to transition from forced PWM mode to pulse skip mode or from pulse skip mode to forced PWM mode, respectively, in two clock cycles.

**Table 5. Mode of Operation**

| SYNC Pin     | Mode of Operation |

|--------------|-------------------|

| Low          | Pulse skip mode   |

| High         | Forced PWM mode   |

| No Connect   | Pulse skip mode   |

| Clock Signal | Forced PWM mode   |

|              |                   |

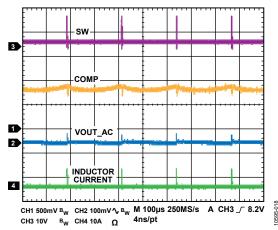

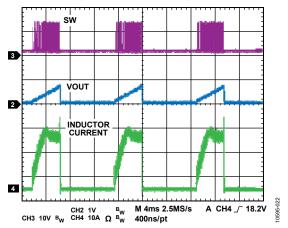

The ADP1851 has pulse skip sensing circuitry that allows the controller to skip PWM pulses, reducing the switching frequency at light loads and, therefore, maintaining better efficiency during light load operation. The resulting output ripple is larger than that of the fixed frequency forced PWM mode. Figure 18 shows the ADP1851 operating in pulse skip mode under a light load. Pulse skip frequency under a light load is dependent on the inductor, output capacitance, output load, and input and output voltages.

Figure 18. Example of Pulse Skip Mode Under a Light Load

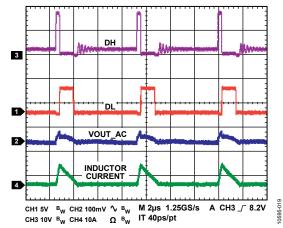

When the output load is greater than the pulse skip threshold current, that is, when  $V_{\text{COMP}}$  reaches the threshold of 0.9 V, the ADP1851 exits the pulse skip mode of operation and enters the fixed frequency discontinuous conduction mode (DCM), as shown in Figure 19. When the load increases further, the ADP1851 enters continuous conduction mode (CCM).

Figure 19. Example of Discontinuous Conduction Mode (DCM) Waveform

In forced PWM mode, the ADP1851 always operates in CCM at any load; therefore, the inductor current is always continuous.

#### SYNCHRONOUS RECTIFIER AND DEAD TIME

In the ADP1851, the antishoot-through circuit monitors the DH to SW and DL to PGND voltages and adjusts the low-side and high-side drivers to ensure break-before-make switching that prevents cross-conduction or shoot-through between the high-side and low-side MOSFETs. This break-before-make switching is known as dead time, which is not fixed and depends on how fast the MOSFETs are turned on and off. In a typical application circuit that uses medium sized MOSFETs with an input capacitance of approximately 3 nF, the typical dead time is approximately 25 ns. When small and fast MOSFETs with fast diode recovery times are used, the dead time can be as low as 13 ns.

#### INPUT UNDERVOLTAGE LOCKOUT

When the bias input voltage at the VIN pin is less than the undervoltage lockout (UVLO) threshold of 2.65 V typical, the switch drivers stay inactive. If EN is high, the controller starts switching and the VIN pin voltage exceeds the UVLO threshold.

#### **INTERNAL LINEAR REGULATOR**

The internal linear regulator is a low dropout (LDO) VCCO. VCCO powers up the internal control circuitry and provides power for the gate drivers. It is guaranteed to have more than 200 mA of output current capability, which is sufficient to handle the gate driver requirements of typical logic threshold MOSFETs driven at up to 1.5 MHz. VCCO is always active and cannot be shut down by the EN signal; however, the over-temperature protection event disables the LDO together with the controller. Bypass VCCO to AGND with a 1  $\mu F$  or greater capacitor.

Because the LDO supplies the gate driver current, the output of VCCO is subject to sharp transient currents as the drivers switch and the boost capacitors recharge during each switching cycle. The LDO has been optimized to handle these transients without overload faults. Due to the gate drive loading, using the VCCO output for other external auxiliary system loads is not recommended.

The LDO includes a current limit that is well above the expected maximum gate driver load. This current limit also includes a short-circuit foldback to further limit the VCCO current in the event of a short-circuit fault.

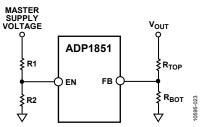

For an input voltage of less than 5.5 V, it is recommended to bypass the LDO by connecting VIN to VCCO, as shown in Figure 20, thus eliminating the dropout voltage. However, if the input range is 4 V to 7 V, the LDO cannot be bypassed by shorting VIN to VCCO because the 7 V input has exceeded the maximum voltage rating of the VCCO pin. In this case, use the LDO to drive the internal drivers, but keep in mind that there is a dropout when  $V_{\rm IN}$  is less than 5 V.

Figure 20. Configuration for  $V_{IN} < 5.5 V$

#### **OVERVOLTAGE PROTECTION**

The ADP1851 has a built-in circuit for detecting output overvoltage at the FB node. When the FB voltage,  $V_{FB}$ , rises above the overvoltage threshold, the high-side N-channel MOSFET (NMOSFET) is turned off, and the low-side NMOSFET is turned on until  $V_{FB}$  drops below the undervoltage threshold. This action is known as the crowbar overvoltage protection. If the overvoltage condition is not removed, the controller maintains the feedback voltage between the overvoltage and undervoltage thresholds, and the output is regulated to within typically +8% and -8% of the regulation voltage. During an overvoltage event, the SS/TRK node discharges through an internal 3  $k\Omega$  pull-down resistor. When the voltage at FB drops below the undervoltage threshold, the soft start sequence restarts. Figure 21 shows the overvoltage protection in PSM.

Figure 21. Overvoltage Protection in PSM Mode,  $V_{OUT}$  Shorted to 2.0 V

#### **POWER GOOD**

The PGOOD pin is an open-drain NMOSFET. An internal  $12.5\,k\Omega$  pull-up resistor is connected between PGOOD and VCCO. PGOOD is internally pulled up to VCCO during normal operation and is active low when triggered. When the feedback voltage,  $V_{FB}$ , rises above the overvoltage threshold or falls below the undervoltage threshold, the PGOOD output is pulled to ground after a delay of  $12~\mu s$ . The overvoltage or undervoltage condition must exist for at least  $10~\mu s$  for PGOOD to become active. The PGOOD output also becomes active if a thermal overload condition is detected.

# SHORT-CIRCUIT AND CURRENT-LIMIT PROTECTION

When the output is shorted or the output current exceeds the current limit set by the current-limit setting resistor (between ILIM and SW) for eight consecutive cycles, the ADP1851 shuts off both the high-side and low-side drivers and restarts the soft start sequence every 10 ms, which is known as hiccup mode. The SS node discharges to zero through an internal 3 k $\Omega$  resistor during an overcurrent or short-circuit event. Figure 22 shows that the ADP1851 on a high current application circuit maintains current-limit hiccup mode when the output is shorted.

Figure 22. Current-Limit Hiccup Mode, 30 A Current Limit

#### **ENABLE/DISABLE CONTROL**

The EN pin is used to enable or disable the ADP1851 controller; the typical precision enable threshold is 0.63 V. When the voltage at EN rises above the threshold voltage, the controller is enabled and starts normal operation after initialization of the internal oscillator, references, settings, and the soft start period. When the voltage at EN falls to typically 30 mV (hysteresis) below the threshold voltage, the driver and the internal controller circuits in the ADP1851 are turned off. The initial settings are still valid; therefore, reenabling the controller does not change the settings until the power at the VIN pin is cycled. In addition, the EN signal does not shut down the LDO regulator at VCCO, which is always active when  $V_{\rm IN}$  is above the UVLO threshold.

For the purpose of start-up power sequencing, the startup of the ADP1851 can be programmed by connecting an appropriate resistor divider from the master power supply to the EN pin, as shown in Figure 23. For example, if the desired start-up voltage from the master power supply is 10 V, R1 and R2 can be set to  $156~\mathrm{k}\Omega$  and  $10~\mathrm{k}\Omega$ , respectively.

Figure 23. Optional Power-Up Sequencing Circuit

#### THERMAL OVERLOAD PROTECTION

The ADP1851 has an internal temperature sensor that senses the junction temperature of the chip. When the junction temperature of the ADP1851 reaches approximately 155°C, the ADP1851 goes into thermal shutdown, the converter is turned off, and the SS/TRK pin discharges toward zero through an internal 3 k $\Omega$  resistor. At the same time, VCCO discharges to zero. When the junction temperature falls below 135°C, the ADP1851 resumes normal operation after the soft start sequence.

### APPLICATIONS INFORMATION

#### **ADIsimPower DESIGN TOOL**

The ADP1851 is supported by the ADIsimPower™ design tool set. ADIsimPower is a collection of tools that produce complete power designs optimized for a specific design goal. The tools allow the user to generate a full schematic and bill of materials and to calculate performance in minutes. ADIsimPower can optimize designs for cost, area, efficiency, and parts count while taking into consideration the operating conditions and limitations of the IC and all real external components. The ADIsimPower tool can be found at www.analog.com/ADIsimPower, and the user can request an unpopulated board through the tool.

#### **SETTING THE OUTPUT VOLTAGE**

The output voltage is set using a resistive voltage divider from the output to FB. For  $R_{BOT}$ , use a 1 k $\Omega$  to 20 k $\Omega$  resistor. Choose  $R_{TOP}$  to set the output voltage by using the following equation:

$$R_{TOP} = R_{BOT} \left( \frac{V_{OUT} - V_{FB}}{V_{FB}} \right)$$

where:

$R_{TOP}$  is the high-side voltage divider resistance.

$R_{BOT}$  is the low-side voltage divider resistance.

$V_{OUT}$  is the regulated output voltage.

$V_{FB}$  is the feedback regulation threshold, 0.6 V.

#### **SOFT START**

The soft start period is set by an external capacitor between SS and AGND. The soft start function limits the input inrush current and prevents output overshoot. When EN is enabled, a current source of  $6.5~\mu A$  starts charging the capacitor, and the regulation voltage is reached when the voltage at SS reaches 0.6~V. The soft start time is approximated by

$$t_{SS} = \frac{0.6 \text{ V}}{6.5 \text{ } \mu\text{A}} C_{SS}$$

The SS pin reaches a final voltage equal to VCCO.

When a controller is disabled, for example, if EN is pulled low or experiences an overcurrent limit condition, the soft start capacitor is discharged through an internal  $3\,\mathrm{k}\Omega$  pull-down resistor.

#### **SETTING THE CURRENT LIMIT**

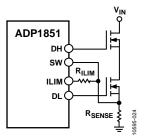

The current-limit comparator measures the voltage across the low-side MOSFET to determine the load current.

The current limit is set by an external current-limit resistor,  $R_{\rm ILIM}$ , between ILIM and SW. The current sense pin, ILIM, sources nominally 50  $\mu A$  to this external resistor. This creates an offset voltage of  $R_{\rm ILIM}$  multiplied by 50  $\mu A$ . When the drop across the current sense element  $R_{CS}$  (low-side MOSFET,  $R_{DSON}$ ) is equal to or greater than this offset voltage, the ADP1851 flags a current-limit event.

$$R_{ILIM} = \frac{1.06 \times I_{LPK} \times R_{CS}}{50 \text{ } \mu\text{A}}$$

where

$I_{LPK}$  is the peak inductor current.

#### **ACCURATE CURRENT-LIMIT SENSING**

The  $R_{DSON}$  of the MOSFET can vary by more than 50% over the temperature range. Accurate current-limit sensing is achieved by adding a current sense resistor from the source of the low-side MOSFET to PGND. Make sure that the power rating of the current sense resistor is adequate for the application. Figure 24 illustrates the implementation of accurate current-limit sensing.

Figure 24. Accurate Current-Limit Sensing

#### INPUT CAPACITOR SELECTION

Use two parallel capacitors placed close to the drain of the high-side switch MOSFET (one bulk capacitor of sufficiently high current rating and a 10  $\mu F$  ceramic decoupling capacitor).

Select the input bulk capacitor based on its ripple current rating. The minimum input capacitance required for a particular load is

$$C_{IN,MIN} = \frac{I_O \times D(1-D)}{(V_{PP} - I_O \times DR_{FSP}) f_{SW}}$$

where:

$I_O$  is the output current.

*D* is the duty cycle.

$V_{PP}$  is the desired input ripple voltage.

$R_{ESR}$  is the equivalent series resistance of the capacitors.

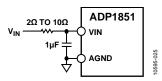

#### **VIN PIN FILTER**

It is recommended that a low-pass filter be connected to the VIN pin. Connecting a resistor, between 2  $\Omega$  and 10  $\Omega$ , in series with VIN and a 1  $\mu F$  ceramic capacitor between VIN and AGND creates a low-pass filter that effectively filters out any unwanted glitches caused by the switching regulator. Keep in mind that the input current may be larger than 100 mA when driving large MOSFETs. A 100 mA current across a 10  $\Omega$  resistor creates a 1 V drop, which is the same voltage drop in VCCO. In this case, a lower resistor value is desirable.

Figure 25. Input Filter Configuration

#### **BOOST CAPACITOR SELECTION**

Connect a boost capacitor between the SW and BST pins to provide the current for the high-side driver during switching. Choose a ceramic capacitor with a value between 0.1  $\mu F$  and 0.22  $\mu F$ .

#### INDUCTOR SELECTION

For most applications, choose an inductor value such that the inductor ripple current is between 20% and 40% of the maximum dc output load current.

Choose the inductor value using the following equation:

$$L = \frac{V_{\mathit{IN}} - V_{\mathit{OUT}}}{f_{\mathit{SW}} \times \Delta I_{\mathit{L}}} \times \frac{V_{\mathit{OUT}}}{V_{\mathit{IN}}}$$

where:

*L* is the inductor value.

$V_{IN}$  is the input voltage.

$V_{OUT}$  is the output voltage.

*f*<sub>SW</sub> is the switching frequency.

$\Delta I_L$  is the peak-to-peak inductor ripple current.

Check the inductor data sheet to make sure that the saturation current of the inductor is well above the peak inductor current of a particular design.

#### **OUTPUT CAPACITOR SELECTION**

For maximum allowed switching ripple at the output, choose an output capacitor that is larger than

$$C_{OUT} \cong \frac{\Delta I_L}{8f_{SW}} \times \frac{1}{\sqrt{\Delta V_{OUT}^2 - \Delta I_L^2 \times (R_{ESR}^2 - (4f_{SW} \times L_{ESL})^2)}}$$

where:

$\Delta I_L$  is the inductor ripple current.

$\Delta V_{OUT}$  is the target maximum output ripple voltage.  $R_{ESR}$  is the equivalent series resistance of the output capacitor (or the parallel combined ESR of all output capacitors).  $L_{ESL}$  is the equivalent series inductance of the output capacitor (or the parallel combined ESL of all capacitors).

The impedance of the output capacitor at the switching frequency multiplied by the ripple current gives the output voltage ripple. The impedance is made up of the capacitive impedance plus the nonideal parasitic characteristics, the equivalent series resistance (ESR), and the equivalent series inductance (ESL).

Usually the capacitor impedance is dominated by ESR. The maximum ESR rating of the capacitor, such as in electrolytic or polymer capacitors, is provided in the manufacturer's data sheet; therefore, the output ripple reduces to

$$\Delta V_{OUT} \cong \Delta I_L \times R_{ESR}$$

Electrolytic capacitors also have significant ESL, on the order of 5 nH to 20 nH, depending on type, size, and geometry. PCB traces contribute some ESR and ESL as well. However, using the maximum ESR rating from the capacitor data sheet usually provides some margin such that measuring the ESL may not be required.

In the case of output capacitors where the impedances of the ESR and ESL are small at the switching frequency, for example, where the output capacitor is a bank of parallel MLCC capacitors, the capacitive impedance dominates; therefore, the output capacitance must be larger than

$$C_{OUT} \cong \frac{\Delta I_L}{8 \, \Delta V_{OUT} \times f_{SW}} \tag{1}$$

Make sure that the ripple current rating of the output capacitors is greater than the maximum inductor ripple current.

To meet the requirement of the output voltage overshoot during load release, the output capacitance should be larger than

$$C_{OUT} \cong \frac{\Delta I_{STEP}^{2} L}{\left(V_{OUT} + \Delta V_{OVERSHOOT}\right)^{2} - V_{OUT}^{2}}$$

(2)

where:

$\Delta V_{OVERSHOOT}$  is the maximum allowed overshoot.

Select the largest output capacitance given by either Equation 1 or Equation 2.

#### MOSFET SELECTION

The choice of MOSFET directly affects the dc-to-dc converter performance. A MOSFET with low on resistance reduces I²R losses, and low gate charge reduces transition losses. The MOSFET should have low thermal resistance to ensure that the power dissipated in the MOSFET does not result in excessive MOSFET die temperature.

The high-side MOSFET carries the load current during on time and usually carries most of the transition losses of the converter. Typically, the lower the on resistance of the MOSFET, the higher the gate charge, and vice versa. Therefore, it is important to choose a high-side MOSFET that balances the two losses. The conduction loss of the high-side MOSFET is determined by the equation

$$P_C = (I_{LOAD(RMS)})^2 \times R_{DSON}$$

where:

$R_{DSON}$  is the MOSFET on resistance.

The gate charging loss is approximated by the equation

$$P_G \cong V_{PV} \times Q_G \times f_{SW}$$

where:

$V_{PV}$  is the gate driver supply voltage.

$Q_G$  is the MOSFET total gate charge.

Note that the gate charging power loss is not dissipated in the MOSFET but rather in the ADP1851 internal drivers. This power loss should be taken into consideration when calculating the overall power efficiency.

The high-side MOSFET transition loss is approximated by the equation

$$P_{\scriptscriptstyle T} \cong \frac{V_{\scriptscriptstyle IN} \times I_{\scriptscriptstyle LOAD} \times (t_{\scriptscriptstyle R} + t_{\scriptscriptstyle F}) \times f_{\scriptscriptstyle SW}}{2}$$

where:

$P_T$  is the high-side MOSFET transition loss power.  $t_R$  is the rise time in charging the high-side MOSFET.  $t_F$  is the fall time in discharging the high-side MOSFET.

t<sub>R</sub> and t<sub>F</sub> can be estimated by

$$t_{R} \cong \frac{Q_{GSW}}{I_{DRIVER\_RISE}}$$

$$t_{\scriptscriptstyle F} \cong \frac{Q_{\scriptscriptstyle GSW}}{I_{\scriptscriptstyle DRIVER\_FALL}}$$

where:

$Q_{\text{GSW}}$  is the gate charge of the MOSFET during switching and is given in the MOSFET data sheet.

*I*<sub>DRIVER\_RISE</sub> and *I*<sub>DRIVER\_FALL</sub> are the driver current outputs from the ADP1851 internal gate drivers.

If  $Q_{GSW}$  is not given in the data sheet, it can be approximated by

$$Q_{GSW} \cong Q_{GD} + \frac{Q_{GS}}{2}$$

where:

$Q_{GD}$  and  $Q_{GS}$  are the gate-to-drain and gate-to-source charges given in the MOSFET data sheet.

IDRIVER RISE and IDRIVER FALL can be estimated by

$$I_{\textit{DRIVER\_RISE}} \cong \frac{V_{\textit{DD}} - V_{\textit{SP}}}{R_{\textit{ON\_SOURCE}} + R_{\textit{GATE}}}$$

$$I_{\textit{DRIVER\_FALL}} \cong \frac{V_{\textit{SP}}}{R_{\textit{ON-SINK}} + R_{\textit{GATE}}}$$

where

$V_{DD}$  is the input supply voltage to the driver and is between 2.75 V and 5 V, depending on the input voltage.

$V_{SP}$  is the switching point where the MOSFET fully conducts; this voltage can be estimated by inspecting the gate charge graph given in the MOSFET data sheet.

*R*<sub>ON\_SOURCE</sub> is the on resistance of the ADP1851 internal driver, given in Table 1, when charging the MOSFET.

$R_{ON\_SINK}$  is the on resistance of the ADP1851 internal driver, given in Table 1, when discharging the MOSFET.

$R_{GATE}$  is the on gate resistance of the MOSFET, given in the MOSFET data sheet. If an external gate resistor is added, add this external resistance to  $R_{GATE}$ .

The total power dissipation of the high-side MOSFET is the sum of the conduction and transition losses:

$$P_{HS} \cong P_C + P_T$$

The synchronous rectifier, or low-side MOSFET, carries the inductor current when the high-side MOSFET is off. The low-side MOSFET transition loss is small and can be ignored in the calculation. For high input voltage and low output voltage, the low-side MOSFET carries the current most of the time. Therefore, to achieve high efficiency, it is critical to optimize the low-side MOSFET for low on resistance. In cases where the power loss exceeds the MOSFET rating or lower resistance is required than is available in a single MOSFET, connect multiple low-side MOSFETs in parallel. The equation for low-side MOSFET conduction power loss is

$$P_{CLS} = (I_{LOAD(RMS)})^2 \times R_{DSON}$$

There is also additional power loss during the time, known as dead time, between the turn-off of the high-side switch and the turn-on of the low-side switch, when the body diode of the low-side MOSFET conducts the output current. The power loss in the body diode is given by

$$P_{\textit{BODYDIODE}} = V_{\textit{F}} \times t_{\textit{D}} \times f_{\textit{SW}} \times I_{\textit{O}}$$

where:

$V_F$  is the forward voltage drop of the body diode, typically 0.7 V.  $t_D$  is the dead time in the ADP1851, typically 25 ns when driving a medium size MOSFET with input capacitance,  $C_{ISS}$ , of approximately 3 nF. The dead time is not fixed. Its effective value varies with gate drive resistance and  $C_{ISS}$ ; therefore,  $P_{BODYDIODE}$  increases in high load current designs and low voltage designs.

Therefore, the power loss in the low-side MOSFET is

$$P_{LS} = P_{CLS} + P_{BODYDIODE}$$

Note that the MOSFET on resistance,  $R_{DSON}$ , increases with increasing temperature, with a typical temperature coefficient of 0.4%/°C. The MOSFET junction temperature ( $T_J$ ) rise over the ambient temperature is

$$T_I = T_A + \theta_{IA} \times P_D$$

where:

$T_A$  is the ambient temperature.

$\theta_{IA}$  is the thermal resistance of the MOSFET package.  $P_D$  is the total power dissipated in the MOSFET.

#### LOOP COMPENSATION—VOLTAGE MODE

Set the controller to voltage mode operation by placing a  $100~k\Omega$  resistor between DL and PGND. Choose the largest possible ramp amplitude for the voltage mode below 1.5 V. The ramp voltage is programmed by a resistor placed between  $V_{\rm IN}$  and the RAMP pin as follows:

$$R_{RAMP} = \frac{V_{IN} - 0.2 \text{ V}}{100 \text{ pF} \times f_{SW} \times V_{RAMP}}$$

The voltage at the RAMP pin is fixed at 0.2 V, and the current going into RAMP should be between 10  $\mu A$  and 160  $\mu A$ . Make sure that the following condition is satisfied:

$$10 \,\mu\text{A} \le \frac{V_{IN} - 0.2 \,\text{V}}{R_{PAMP}} \le 160 \,\mu\text{A} \tag{3}$$

For example, with an input voltage of 12 V,  $R_{\text{RAMP}}$  should not be less than 73.8  $k\Omega.$

Assuming that the LC filter design is complete, the feedback control system can be compensated. In general, aluminum electrolytic capacitors have high ESR; however, if several aluminum electrolytic capacitors are connected in parallel and produce a low effective ESR, then Type III compensation is needed. In addition, ceramic capacitors have very low ESR (only a few milliohms), making Type III compensation a better choice.

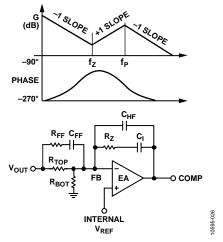

#### Type III Compensation

Figure 26. Type III Compensation

If the output capacitor ESR zero frequency is greater than onehalf of the crossover frequency, use the Type III compensator as shown in Figure 26.

Calculate the output LC filter resonant frequency as follows:

$$f_{LC} = \frac{1}{2\pi\sqrt{LC}} \tag{4}$$

Choose a crossover frequency that is 1/10 of the switching frequency:

$$f_{\rm CO} = \frac{f_{\rm SW}}{10} \tag{5}$$

Set the poles and zeros as follows:

$$f_{PI} = f_{P2} = \frac{1}{2} f_{SW} \tag{6}$$

$$f_{ZI} = f_{Z2} = \frac{f_{CO}}{4} = \frac{f_{SW}}{40} = \frac{1}{2\pi R_z C_I}$$

(7)

or

$$f_{ZI} = f_{ZZ} = \frac{f_{LC}}{2} = \frac{1}{2\pi R_{\nu}C_{I}}$$

(8)

Use the lower zero frequency from Equation 7 or Equation 8. Calculate the compensation resistor,  $R_{\rm Z}$ , as follows:

$$R_{Z} = \frac{R_{TOP} V_{RAMP} f_{ZI} f_{CO}}{V_{IN} f_{LC}^{2}}$$

(9)

Next, calculate C<sub>I</sub>.

$$C_{I} = \frac{1}{2\pi R_{z} f_{z_{I}}} \tag{10}$$

Because of the finite output current drive of the error amplifier,  $C_I$  must be less than 10 nF. If it is larger than 10 nF, choose a larger  $R_{TOP}$  and recalculate  $R_Z$  and  $C_I$  until  $C_I$  is less than 10 nF.

Because C<sub>HF</sub> << C<sub>I</sub>, calculate C<sub>HF</sub> as follows:

$$C_{HF} = \frac{1}{\pi f_{SW} R_Z} \tag{11}$$

Next, calculate the feedforward capacitor,  $C_{FF}$ , assuming  $R_{FF} << R_{TOP}$ .

$$R_{FF} = \frac{1}{\pi C_{FF} f_{SW}} \tag{12}$$

Check that the calculated component values are reasonable. For example, capacitors smaller than about 10 pF should be avoided. In addition,  $R_Z$  values less than 3  $k\Omega$  and  $C_I$  values greater than 10 nF should be avoided. If necessary, recalculate the compensation network with a different starting value for  $R_{\text{TOP}}.$  If  $R_Z$  is too small or  $C_I$  is too big, start with a larger value for  $R_{\text{TOP}}.$  This compensation technique should yield a good working solution.

When precise compensation is needed, use the ADIsimPower design tool.

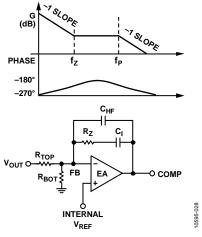

#### LOOP COMPENSATION—CURRENT MODE

Compensate the ADP1851 error voltage loop in current mode using Type II compensation.

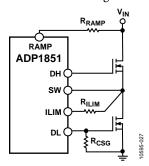

#### **Setting the Slope Compensation**

In a current mode control topology, slope compensation is needed to prevent subharmonic oscillations in the inductor current and to maintain a stable output. The external slope compensation is implemented by summing the amplified sense signal and a scaled voltage at the RAMP pin. To set the effective slope compensation, connect a resistor ( $R_{RAMP}$ ) between the RAMP pin and the input voltage ( $V_{IN}$ ).  $R_{RAMP}$  is calculated by

$$R_{RAMP} = \frac{7 \times 10^6 \times L}{A_{CS} \times R_{CS}}$$

where:

L is the inductor value measured in  $\mu$ H.

$R_{CS}$  (m $\Omega$ ) is the resistance of the current sense element between SW and PGND ( $R_{DSON\_MAX}$  is the low-side MOSFET maximum on resistance).

$A_{CS}$  is the current sense amplifier gain and is 3 V/V, 6 V/V, or 12 V/V.

Thus, the voltage ramp amplitude, V<sub>RAMP</sub>, is:

$$V_{RAMP} = \frac{V_{IN} - 0.2 \text{ V}}{100 \text{ pF} \times f_{SW} \times R_{RAMP}}$$

where 100 pF is the effective capacitance of the internal ramp capacitor,  $C_{RAMP}$ , with  $\pm 4\%$  tolerance over the temperature and  $V_{IN}$  range.

The voltage at the RAMP pin is fixed at 0.2 V, and the current going into RAMP should be between 10  $\mu A$  and 160  $\mu A$ . Make sure that the following condition is satisfied:

$$10 \,\mu\text{A} \le \frac{V_{IN} - 0.2 \,\text{V}}{R_{PAMP}} \le 160 \,\mu\text{A}$$

For example, with an input voltage of 12 V,  $R_{RAMP}$  should not exceed 1.1  $M\Omega.$  If the calculated  $R_{RAMP}$  value produces less than 10  $\mu A$ , then select an  $R_{RAMP}$  value that produces between 10  $\mu A$  and 15  $\mu A$ .

Figure 27 illustrates the connection of the slope compensation resistor,  $R_{RAMP}$ , and the current sense gain resistor,  $R_{CSG}$ .

Figure 27. Slope Compensation and CS Gain Connection

#### **Setting the Current Sense Gain**

The voltage drop across the external low-side MOSFET is sensed by a current sense amplifier by multiplying the peak inductor current and the  $R_{\rm DSON}$  of the MOSFET. The result is then amplified by a gain factor of 3 V/V, 6 V/V, or 12 V/V, which is programmable by an external resistor,  $R_{\rm CSG}$ , connected to the DL pin. This gain is sensed only during power-up and not during normal operation. The amplified voltage is summed with the slope compensation ramp voltage and fed into the PWM controller for a stable regulation voltage.

The voltage range of the internal node,  $V_{\text{CS}}$ , is between 0.4 V and 2.2 V. Select the current sense gain such that the internal minimum amplified voltage ( $V_{\text{CSMIN}}$ ) is above 0.4 V and the maximum amplified voltage ( $V_{\text{CSMAX}}$ ) is 2.1 V. Note that  $V_{\text{CSMIN}}$  or  $V_{\text{CSMAX}}$  is not the same as  $V_{\text{COMP}}$ , which has a range of 0.9 V to 2.2 V. Make sure that the maximum  $V_{\text{COMP}}$  ( $V_{\text{COMPMAX}}$ ) does not exceed 2.2 V to account for temperature and part-to-part variations. See the following equations for  $V_{\text{CSMIN}}$ ,  $V_{\text{CSMAX}}$ , and  $V_{\text{COMPMAX}}$ .

$$\begin{split} V_{CSMIN} &= 0.75 \text{ V} - \frac{1}{2}I_L \times R_{DSON\_MIN} \times A_{CS} \\ V_{CSMAX} &= 0.75 \text{ V} + (I_{LOADMAX} - \frac{1}{2}I_L) \times R_{DSON\_MAX} \times A_{CS} \\ V_{COMPMAX} &= \frac{(V_{IN} - 0.2 \text{ V}) \times t_{ON}}{100 \text{ pF} \times R_{BAMR}} + V_{CSMAX} \end{split}$$

where:

$V_{\it CSMIN}$  is the minimum amplified voltage of the internal current sense amplifier at zero output current.

$I_L$  is the peak-to-peak ripple current in the inductor.  $R_{DSON\_MIN}$  is the low-side MOSFET minimum on resistance. The zero current level voltage of the current sense amplifier is 0.75 V.  $V_{CSMAX}$  is the maximum amplified voltage of the internal current

$I_{LOADMAX}$  is the maximum output dc load current.  $R_{DSON\_MAX}$  is the low-side MOSFET maximum on resistance.  $A_{CS}$  is the current sense amplifier gain.

sense amplifier at the maximum output current.

$V_{COMPMAX}$  is the maximum voltage at the COMP pin.  $t_{ON}$  is the high-side driver (DH) on time.

Replace  $R_{DSON}$  with the resistance value of the current sense element,  $R_{CS}$ , if it is used.

#### Type II Compensation

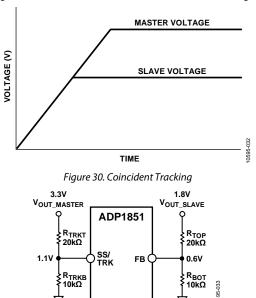

Figure 28. Type II Compensation